# MM65K Memory Board User's Manual

# TABLE OF CONTENTS

\_\_\_\_\_\_

•

| 1. | INTRODUCTION                                                                                                                                                                                                                                                                                    | 1                                       |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 2. | OVERVIEW                                                                                                                                                                                                                                                                                        | 2                                       |

| 3. | SPECIFICATIONS                                                                                                                                                                                                                                                                                  | 3                                       |

| 4. | <pre>INSTALLATION PROCEDURES.<br/>4.1. ENABLES AND PHANTOM.<br/>4.1.1. ENABLE/DISABLE AT POWER ON CLEAR OR RESET.<br/>4.1.2. PHANTOM.<br/>4.2. MEMORY CONFIGURATION.<br/>4.2.1. MEMORY ADDRESSING.<br/>4.2.2. 2K SEGMENT DISABLE.<br/>4.2.3. EXTENDED ADDRESSING.<br/>4.2.4. BANK SELECT.</pre> | <b>4</b><br>4<br>5<br>6<br>7<br>9<br>1Ø |

|    | SPECIAL APPLICATION NOTES.<br>5.1. USING PROMS.<br>5.2. DISABLING BLOCKS OF MEMORY.<br>5.3. 32K/48K MAPPING.<br>5.4. MULTIPLE BANK CONTROL FEATURE.<br>5.5. INTERFACING WITH NON IEEE STANDARD SYSTEMS.                                                                                         | 12<br>12<br>12<br>13<br>14              |

| 6. | SUBJECT INDEX                                                                                                                                                                                                                                                                                   | 15                                      |

# LIST OF FIGURES

| 1-1.              | RESET AND POJ CONFIGURATION HEADER                 | 4  |

|-------------------|----------------------------------------------------|----|

|                   |                                                    | 4  |

| 4-2:              | POJ AND RESET CONFIGURATIONS                       | 4  |

| 4-3:              | PHANTOM CONFIGURATION HEADERS                      | 5  |

| 4-4:              | PHANTOM CONFIGURATIONS                             | 5  |

| 4-5:              | ASSIGNMENT OF INDIVIDUAL 16K BLOCKS OF MEMORY      | 6  |

| 4-6:              | EXAMPLE OF STANDARD 64K CONFIGURATION              | 7  |

| 4-7:              | EXAMPLE OF 64K CONFIGURATION W/2K REMOVED AT F800  | 8  |

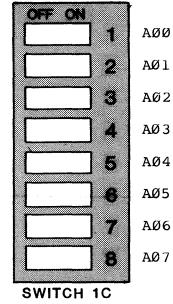

| 4-8:              | DIP SWITCH 1C USED WITH EXTENDED ADDRESSING        | 9  |

| 4-9:              | EXAMPLE OF EXTENDED ADDRESSING @ Ø3ØØØØH - Ø3FFFFH | 1Ø |

| 4-10:             | DIP SWITCH 1C USED WITH BANK SELECT                | 11 |

| 4-11:             | EXAMPLE OF BOARD SETUP FOR BANK SELECT             | 11 |

| the second second | an an ann an an an ann ann ann ann ann             |    |

| 5-1:              | EXAMPLE OF MULTIPLE BANK CONTROL                   | 13 |

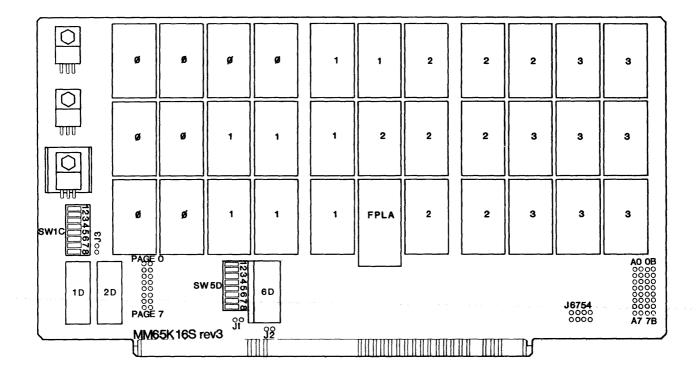

COMPONENT LAYOUT DIAGRAM

## LIST OF TABLES

| 4-1: | MEMORY ADDRESSING TABLE  | 6  |

|------|--------------------------|----|

| 4-2: | 2K SEGMENT DISABLE TABLE | 8  |

|      |                          | -  |

| 5-1. | 32/48K MAPPING TABLE     | 10 |

| 2-1: | 52/40K MAPPING IADLE     | 12 |

#### 1. INTRODUCTION

Bank select, PHANTOM, extended addressing, fast access time, low power consumption, and IEEE compatible are some of the words that are used to describe Memory products. We at Morrow Designs have made these words a reality with the introduction of the Morrow Designs MM65K16S Memory Board.

The Morrow Designs MM65K16S Static RAM is, without a doubt the most versatile memory board on the market today. With so many features at a price that is affordable, the MM65K16S is an unsurpassed value.

Bank select or extended addressing; you have a choice. The bank select feature is switch setable to any one of 256 available I/O addresses and will respond to any one or combination of the eight data bits that are desired. Extended addressing allows the MM65Kl6S to reside anywhere in the memory map with no imposed limitations by the addressing range of the microcomputer system.

The MM65K16S draws an average of 500 milliamps (Ma) of current with code executing in RAM and some boards have measured considerably less under the same circumstances. With such a low current drain, it is obvious that only 1 regulator is needed, but for those planning to use a programmed 2716 EPROM or equivalent PROM, extra current demands can easily be met by the three on board regulators. For those dedicated applications where both RAM and ROM are needed, the MM65K16S RAM Board really fits the bill.

The Morrow Designs MM65Kl6S is guaranteed to run with any 8080, Z80, or 8085 processor on the market today. This includes some of the new 6 MHZ processors that are beginning to surface. In fact, the MM65Kl6S is guaranteed to run reliably with processors that have clock speeds up to 6 MHZ.

#### 2. OVERVIEW

Before installing the memory board, please read the instructions in this manual. The Morrow Designs MM65Kl6S is a very sophisticated RAM board and has many options that must be set correctly for proper operation of the system.

Chapter 4 - INSTALLATION PROCEDURES - is an introduction to the Morrow Designs MM65Kl6S Static RAM board. It deals with the configuration, features, and use of the board. This section provides elaborate coverage of all the most used features and provides a great number of examples to help simplify the set up and testing of the board.

Chapter 5 - SPECIAL APPLICATION NOTES - deals with what the Morrow Designs call "the nice little things to know". This section deals with the special application notes that are necessary for only a few users, but can save time and money in the long run when the system in use has a need for one of these particular features.

WARNING....NEVER INSERT OR REMOVE THE MORROW DESIGNS OR ANY OTHER BOARD WITH POWER ON. ALWAYS REMOVE POWER FROM THE BUS AS SERIOUS ELECTRICAL DAMAGE COULD OCCUR TO THE SYSTEM AND THE BOARD OR BOARDS THAT WERE REMOVED OR INSTALLED.

#### 3. SPECIFICATIONS

#### SPECIFICATIONS FOR THE MORROW DESIGNS MM65K16S

#### **POWER REQUIREMENTS:**

8V @ 55Ø-625 MAX 35Ø MA TYPICAL +/- 16V NOT USED

#### RAM CHIPS:

M58725P OR EQUIV 2K X 8 ORGANIZATION 5 MA DESELECTED 40 MA SELECTED 150 NS ACCESS TIME OR BETTER

#### SPECIAL COMPONENTS:

| 825100 | FPLA | CUSTOM | PROGRAMMED | PART |

|--------|------|--------|------------|------|

| 16L2   | PAL  | CUSTOM | PROGRAMMED | PART |

| 14L4   | PAL  | CUSTOM | PROGRAMMED | PART |

#### **FEATURES:**

- \*\* OPERATION GUARANTEED AT 6 MHZ

- \*\* IEEE 696 (S-100) COMPATIBLE

- \*\* LOW POWER CONSUMPTION

- \*\* EXTENDED ADDRESSING

- \*\* BANK SELECT

- \*\* TWO INDEPENDENT 32K BANKS OF MEMORY

- \*\* 2K SEGMENT DISABLE

\*\* PHANTOM

- \*\* MULTIPLE BANK CONTROL FEATURE

- \*\* PROM SUBSTITUTION FOR SPECIAL APPLICATIONS

- \*\* ENABLE/DISABLE AT POWER ON OR RESET

#### 4. <u>INSTALLATION</u> <u>PROCEDURES</u> <u>4.1.</u> <u>ENABLES AND</u> <u>PHANTOM</u> <u>4.1.1.</u> <u>ENABLE/DISABLE AT</u> POWER ON CLEAR OR RESET

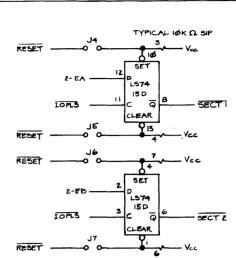

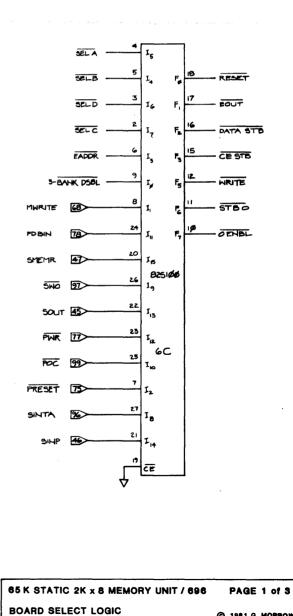

The MM65Kl6S memory board can be divided into two "banks" of memory that can be enabled or disabled when POWER ON CLEAR or RESET are in an active state. In order for all 64K of memory to be active on the bus both "Banks" of memory must be configured to enable in response to either POWER ON CLEAR or RESET.

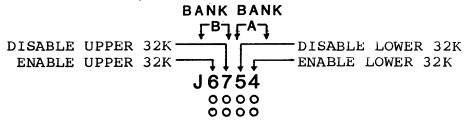

An 8-pin header is located under IC 15D (74LS74) and is used to set the board so that either one or both of the banks of memory will be enabled or disabled whenever RESET or POWER ON CLEAR are active on the bus. This header is labeled J6~7~5~4 and is configured by shunts that are placed across the row of pins.

The diagram below shows the jumper indications and the bank of memory that each jumper controls.

Figure 4-1: RESET AND POJ CONFIGURATION HEADER

The following examples indicate the four possible settings for the enable/disable feature.

BOTH 32K BANKS ENABLED

BOTH 32K BANKS DISABLED

UPPER 32K DISABLED LOWER 32K ENABLED UPPER 32K ENABLED LOWER 32K DISABLED

Figure 4-2: POJ AND RESET CONFIGURATIONS

CAUTION: DO NOT INSTALL SHUNT JUMPERS ACROSS (J4 AND J5) OR (J6 AND J7) AT THE SAME TIME, AS UNPREDICTABLE RESULTS COULD OCCUR.

#### 4.1.2. PHANTOM

The PHANTOM option is used to remove a section or sections memory from the bus during specific operations. Some of these operations might include the enabling of a bootstrap loader, ROM monitor, or a POWER ON JUMP function.

Because there are two 32K banks of memory, it is necessary to configure the MM65K15S for proper operation with PHANTOM. Because both the upper and lower 32K banks of RAM individually respond to PHANTOM, it is mandatory that the MM65K16S be properly configured to recognize or ignore the PHANTOM signal.

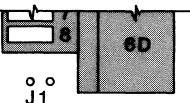

The headers labeled J1 and J2 control PHANTOM. The J1 header is located directly below the DIP switch at 5D and controls PHANTOM for the upper 32K of memory. J2 is located directly below the IC in location 6D and controls the PHANTOM for the lower 32K of memory. As in the enable/disable circuitry, the mode is set by the use of shunts.

The following table shows the PHANTOM configuration header and the proper bank each jumper represents.

(BANK B) UPPER 32K

O O J2 LOWER 32K (BANK A)

#### Figure 4-3: PHANTOM CONFIGURATION HEADERS

The following examples indicate the four possible ways that PHANTOM can be set for response.

Figure 4-4: PHANTOM CONFIGURATIONS

#### 4.2. <u>MEMORY CONFIGURATION</u> 4.2.1. <u>MEMORY ADDRESSING</u>

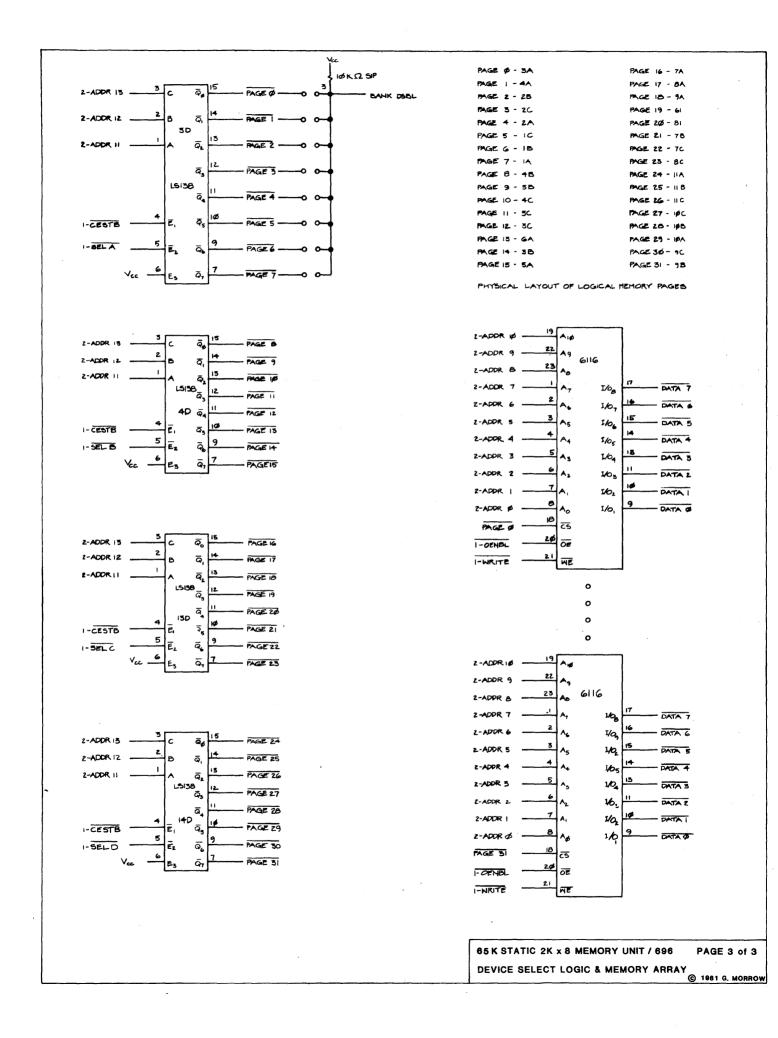

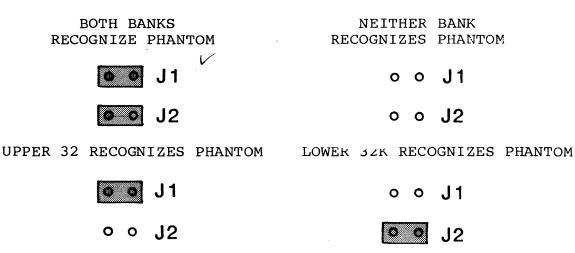

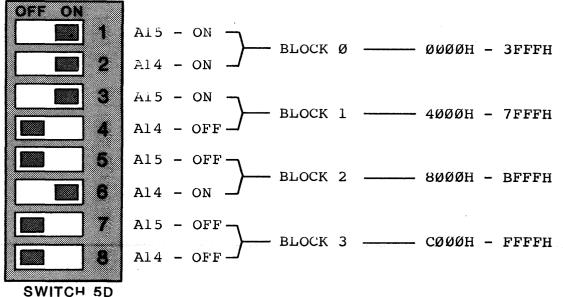

The Morrow Designs MM65Kl6S memory board is configured as four individual 16K blocks of memory. Each of these four blocks can be located on any 16K boundary. Thus, blocks of memory can be assigned at address ØØØØH, 4000H, 8000H, or CØØØH.

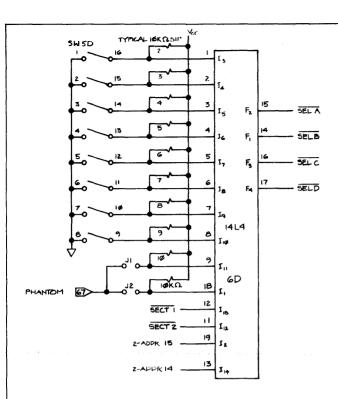

The DIP switch array located at 5D determines the addressing of the memory board. The DIP switch uses a binary counting system to determine which one of the four blocks will reside on a specific boundary in the memory map.

The table below shows memory addressing:

| A15 | Al4 | BLOCK # | ADDRESS FROM - TO | BANK |

|-----|-----|---------|-------------------|------|

| ON  | ON  | Ø       | ØØØØH - 3FFFH     | А    |

| ON  | OFF | 1       | 4000H - 7FFFH     | А    |

| OFF | ON  | 2       | 8000H - BFFFH     | В    |

| OFF | OFF | 3       | CØØØH – FFFFH     | Б    |

#### Table 4-1: MEMORY ADDRESSING TABLE

The table below shows the relationship between the switch settings on the DIP switch at location 5D and the assignment of the individual 16K blocks of memory.

Figure 4-5: ASSIGNMENT OF INDIVIDUAL 16K BLOCKS OF MEMORY

The following examples will show the proper configuration for the memory board so that it will occupy a full 64K compliment.

#### Figure 4-6: EXAMPLE OF STANDARD 64K CONFIGURATION

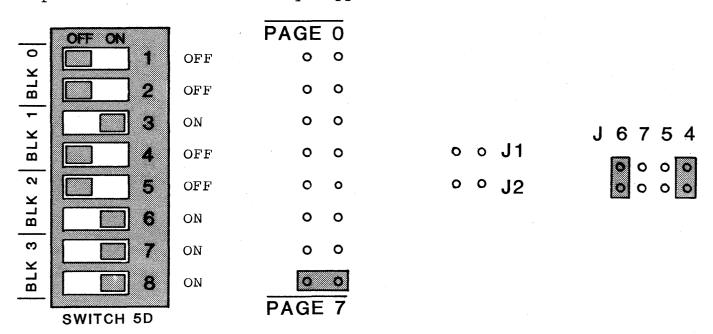

#### 4.2.2. 2K SEGMENT DISABLE

The MM65K16S RAM board is capable of disabling a 2K segment of memory anywhere in the memory map. This feature is necessary in systems that might include a memory mapped disk controller or memory mapped video display interface.

The 2K disable feature is assigned to BLOCK Ø (paddle 1 and 2 on switch located at 5D. Because each 16K block can be addressed anywhere within the memory map, if a 2K hole is needed in the memory map were BLOCK 3 is normally addressed, simply reverse the addressing switches and locate BLOCK 3 where BLOCK Ø was addressed and re-address BLOCK Ø to reside where BLOCK 3 was addressed.

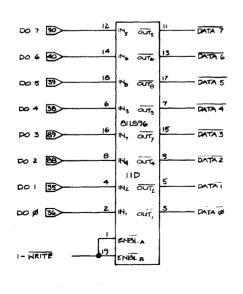

A 16-pin header (dual 8) is located between IC 2D and IC 3D and is used to select the 2K segment that is to be removed from the memory map. This header is labeled **PAGE** Ø at the top of the header and labeled **PAGE** 7 at the bottom of the header. The PAGE number corresponds to the PAGE in memory that is to be disabled by the placement of a shunt across the header.

#### INSTALLATION PROCEDURES

#### MORROW DESIGNS 65K RAM

| PAGE | IC | BLOCK Ø   | BLOCK 1   | BLOCK 2   | BLOCK 3   |

|------|----|-----------|-----------|-----------|-----------|

|      |    | ØØØØ-3FFF | 4000-7FFF | 8000-BFFF | CØØØ-FFFF |

| Ø    | ЗA | ØØØØ-07FF | 4000-47FF | 8000-87FF | CØØØ-C7FF |

| 1    | 4A | Ø8ØØ-ØFFF | 4800-4FFF | 8800-8FFF | C8ØØ-CFFF |

| 2    | 2B | 1000-17FF | 5000-F7FF | 9000-97FF | DØØØ-D7FF |

| 3    | 2C | 1800-1FFF | 5800-5FFF | 98Ø0-9FFF | D8ØØ-DFFF |

| 4    | 2A | 2000-27FF | 6000-67FF | AØØØ-A7FF | EØØØ-E7FF |

| 5    | 10 | 28ØØ-2FFF | 68ØØ-6FFF | A8ØØ-AFFF | E8ØØ-EFFF |

| 6    | 1B | 3000-37FF | 7ØØØ-77FF | BØØØ-B7FF | FØØØ-F7FF |

| 7    | 1A | 38ØØ-3FFF | 7800-7FFF | B800-BFFF | F8ØØ-FFFF |

The table below shows all possible 2K segment disables:

Table 4-2: 2K SEGMENT DISABLE TABLE

The table above is designed to provide a quick and accurate method of determining the proper location of a 2K segment. For example, if the shunt is placed across PAGE 5 and BLOCK  $\emptyset$  is addressed as BLOCK  $\emptyset$ , then memory disabled would be in the address range of 2800 to 2FFF. In the same manner if the shunt was placed across PAGE 7 and BLOCK  $\emptyset$  is addressed as BLOCK 3, then the 2K segment would be disabled from F800 to FFFF.

The following example shows a 2K segment removed at F800 to provide a hole for a memory mapped controller.

Figure 4-7: EXAMPLE OF 64K CONFIGURATION W/2K REMOVED AT F800

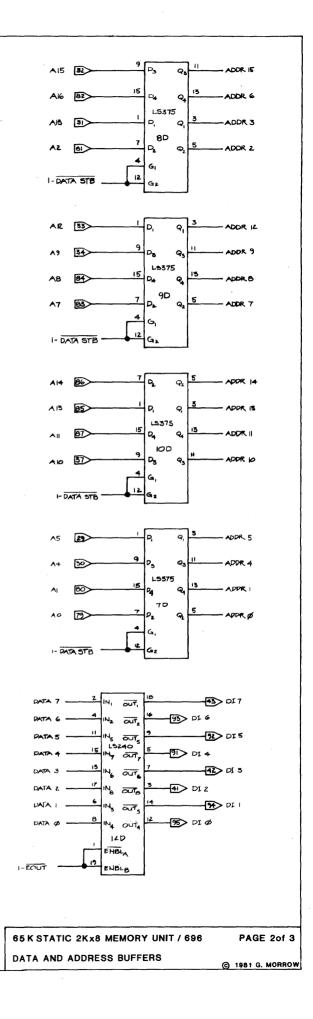

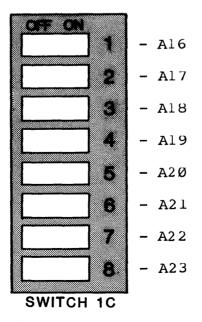

#### 4.2.3. EXTENDED ADDRESSING

The Morrow Designs MM65Kl6S conforms to the latest IEEE S-100 standard, and can therefore recognize all 24 address lines that are available on the S-100 bus. Use of extended addressing does away with the 64K limitation imposed by most microcomputer systems.

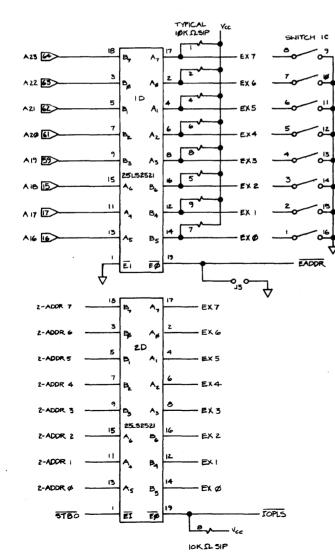

In order for extended addressing to be enabled, location 1D must have a 25LS2521 IC installed. This IC, if not already in location 1D, will probably be found in location 2D (bank select) and should be removed from 2D and reinstalled in location 1D.

Adjacent to the DIP switch 1C is a header labeled **J3.** This header should NOT have a shunt placed across it unless the board is to be set up for bank select. If there is a shunt placed across J3, it should be removed for proper operation of extended addressing.

Once the 25LS2521 is installed at location 1D and the shunt has been removed from the header at location J3, extended addressing is now activated and bank select has been disabled.

The DIP switch that is located at lC is used to set the extended addressing for the memory board. By setting the paddles to the OFF position the associated address line is then recognized when it is in its active state.

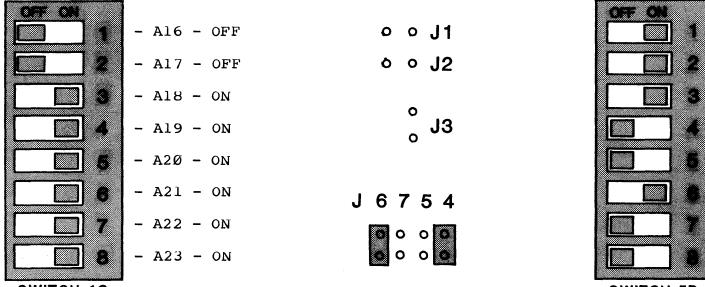

Extended addressing allows the MM65Kl6S RAM board to be addressed in 64K increments starting at address 000000H, 010000H, 020000H, up to FF0000H. The DIP switch that is located at 5D then addresses the 64K banks of memory within the extended addressing range. The example below shows the DIP switch at location 1C and its relationship with the incoming address lines.

Figure 4-8: DIP SWITCH 1C USED WITH EXTENDED ADDRESSING

#### MORROW DESIGNS 65K RAM

The following example indicates the proper switch settings for extended addressing. The board will be set for address Ø3ØØØØH.

SWITCH 1C

SWITCH 5D

#### Figure 4-9: EXAMPLE OF EXTENDED ADDRESSING @ Ø3ØØØØH - Ø3FFFFH

#### 4.2.4. BANK SELECT

For many existing systems designed before the implementation of the IEEE S-100 standard, the use of bank select was mandatory in order to expand memory beyond the 64K limitations. Using a DIP switch and shunt jumpers the MM65K16S RAM board is capable of being configured as any one of 256 I/O ports available, and can enable or disable itself using any one or a combination of the eight data bits available.

In order for bank select to function properly, there must be a 25LS2521 installed in location 2D. If the 25LS2521 is not installed in location 2D, then it will probably be found in location 1D (extended addressing). In any case, it must be installed in location 2D for bank select to function properly.

The next jumper to check is located adjacent to the DIP switch at location 1C on the board. This jumper is labeled **J3** and should have a shunt jumper across it. If there is no jumper across J3, one should be installed, otherwise bank select will not function properly.

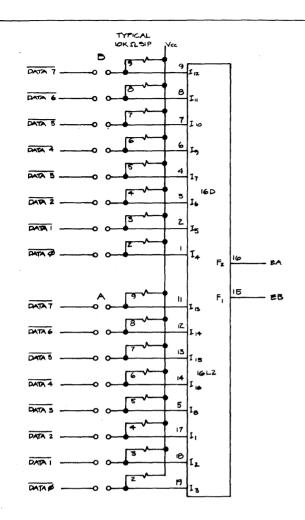

The third and final check, is the setting of the data bit or bits that will enable or disable the individual banks of memory. There are two headers necessary for configuration. These two headers are located on the lower right hand corner of the board adjacent to IC 16D and are labeled  $\mathbf{A} \ \mathbf{\emptyset}$  and  $\ \mathbf{\emptyset} \ \mathbf{B}$  at the top of the header blocks and  $\mathbf{A} \ \mathbf{7}$  and  $\ \mathbf{7} \ \mathbf{B}$  at the bottom of the headers. Bits AØ through A7 control the lower 32K bank of memory and bits ØB through 7B control the upper 32K bank of memory.

#### MORROW DESIGNS 65K RAM

It is important to remember that all switch settings in the bank select configuration are set to the software that is being used. If the operating system does bank select at port 40H, then the MM65K16S RAM board must be configured to run at port 40H also. The following diagram shows the address lines in relation to the DIP switch at location IC.

Figure 4-10: DIP SWITCH 1C USED WITH BANK SELECT

In the following diagram the memory board will be configured for port 40H in the bank select mode and data bit-0 will be used to enable both banks of memory.

| OFF ON    | - AØØ - ON  | ○ ○ J1        |   | 0 | 0 | B |

|-----------|-------------|---------------|---|---|---|---|

| 2         | - AØ1 - ON  | o o <b>J2</b> | 0 | ο | o | 0 |

| 3         | - AØ2 - ON  |               | ο | ο | ο | ο |

| 4         | - AØ3 - ON  | J3            | ο | ο | 0 | 0 |

| 5         | - AØ4 - ON  |               | ο | ο | 0 | 0 |

| 8         | - AØ5 - ON  | J 6 7 5 4     | 0 | ο | ο | 0 |

| 7         | - AØ6 - OFF | 000           | 0 | ο | 0 | ο |

| 8         | - AØ7 - ON  | 000           | 0 | 0 | о | 0 |

| SWITCH 1C | I           |               | A | 7 | 7 | B |

Figure 4-11: EXAMPLE OF BOARD SETUP FOR BANK SELECT

11

#### 5. SPECIAL APPLICATION NOTES

The purpose of this section is to describe some of the problems that could arise when using the board for applications where special types of configurations are necessary. This section will also describe some of the unique features of the MM65Kl6S memory board.

#### 5.1. USING PROMS

When using a programmed 2716 EPROM or equivalent PROM, it is necessary to remember that the MM65K16S memory board **DOES NOT** generate any type of wait states for the processor. Therefore, it is mandatory that the PROMS being used are fast enough. If a 4 Mhz processor is being used, then the PROM must have an access time for 300 ns or faster. Using a slower PROM is almost a certain guarantee of problems.

#### 5.2. DISABLING BLOCKS OF MEMORY

The Morrow Designs MM65K16S disables in 32K banks. Therefore, if it is necessary to disable smaller portions of memory, the board can not be used except by depopulation of the board. If the board is to be depopulated for any reason, that bank of RAM must have the PHANTOM enabled. Failure to activate PHANTOM will cause problems because, even though the memory chips were removed from their sockets, they are still active on the bus.

#### 5.3. 32K/48K MAPPING

When the memory is purchased as a 32K board, it is set up as one 32K bank that utilizes BLOCK  $\emptyset$  and BLOCK 1 of the memory board. If the board is purchased as a 48K board, then BLOCKS  $\emptyset$ ,1, and 2 will be stuffed and BLOCK 3 will be left unstuffed. If the user decides that two 16K blocks of memory are necessary the tables below will indicate which RAM chip is to be installed into what location on the board for any specific block of memory.

BLOCK Ø

1A, 1B, 1C, 2A, 2B, 2C, 3A, 4A

BLOCK 1

3B, 3C, 4B, 4C, 5A, 5B, 5C, 6A

BLOCK 2

6B, 7A, 7B, 7C, 8A, 8B, 8C, 9A

BLOCK 3

9B, 9C, 1ØA,1ØB, 1ØC, 11A, 11B, 11C

Table 5-1: 32/48K MAPPING TABLE

12

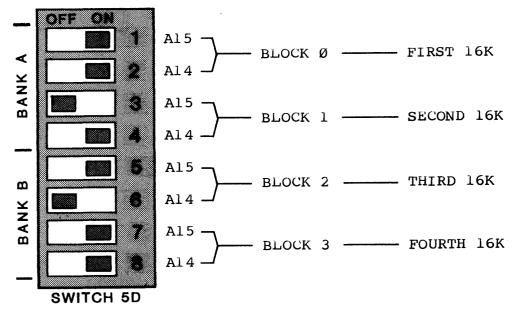

#### 5.4. MULTIPLE BANK CONTROL FEATURE

One of the more interesting features of the MM65K16S is the manner in which the bank select feature operates. The MM65K16S allows for a total of eight independent users, but by using multiple data bits, one bank of memory can be "forced" to follow other banks of memory, or one board could control multiple banks of memory.

The example below is an example of how the multiple bank feature functions. The data bits for AØ to A7 are set up to represent a data pattern of 83H. Data bits ØB to B7 are set up to represent a data pattern of Ø3H.

| A  | 0 | OB |   |  |

|----|---|----|---|--|

| 0  |   | 0  | 0 |  |

|    | 0 | 0  |   |  |

| 0  | 0 | 0  | 0 |  |

| 0  | 0 | 0  | 0 |  |

| 0  | 0 | 0  | 0 |  |

| 0  | 0 | 0  | 0 |  |

| 0  | 0 | 0  | 0 |  |

|    | C | 0  | 0 |  |

| A7 |   | 7  | B |  |

#### Figure 5-1: EXAMPLE OF MULTIPLE BANK CONTROL

In the above example, data bits  $\emptyset$  and 1 were enabled on both the upper and lower banks of memory. The lower bank of memory had data bit-7 set also, and this should be noted.

Whenever the system software issues a bank select command and the data that is sent to the board is equal to the strapping of the data bits, the board will then enable or disable.

The upper bank of memory will respond to data that is equal to Ø3H (bits Ø and 1), but it will also respond to ANY data pattern that has data bits Ø and 1 set. In other words, this Bank will respond to data patterns of Ø3H, Ø7H, 83H, 13H, 4BH, 6FH etc. With this in mind, it is possible for the system software to issue one bank select command and control multiple banks of memory.

The lower bank of memory, (remember data bit-07 was set) is set to recognize a data pattern of 83H, but will respond to any data

#### MORROW DESIGNS MM65K

that has bits  $\emptyset$ , l, and 7 set. So, the lower bank of memory could be set to enable or disable when the system software issues a bank select command and the data patterns are 93H, A3H, F3H, or B7H. Therefore, this bank responds to the system commands in the same fashion as the upper bank responded.

#### 5.5. INTERFACING WITH NON IEEE STANDARD SYSTEMS

The Morrow Designs MM65Kl6S is an IEEE standard board, therefore all control lines must be present on the bus in order for the RAM to function correctly. Some manufacturers do not use the signal SWO (pin-97) which the MM65Kl6S requires to operate correctly. In the event of any difficulty, contact the factory immediately.

#### 6. SUBJECT INDEX

```

2

2K SEGMENT DISABLE, 7

2K SEGMENT

block assignment of, 7

```

#### B

BANK SELECT, 10 BLOCK 0, 7 bank control multiple, 13

#### D

DIP SWITCH 1C as bank select, 10 1C as extended addressing, 9 5D to set up block addresses, 6

#### E

ENABLE/DISABLE AT POWER ON CLEAR OR RESET, 4 EXTENDED ADDRESSING, 9

#### $\mathbf{F}$

features, 3

#### Η

HEADER PAGE Ø thru PAGE 7, 7 setting of AØØB, 1Ø

# $\frac{I}{IC}$

15D, 4 25LS2521 in bank select, 10 25LS2521 in extended addressing, 9

#### J J1, 5 J2, 5 J3, 9 Use with bank select, 10 Use with extended addressing, 9 J6 7 5 4, 4

#### MORROW DESIGNS 65K RAM

#### M

MEMORY ADDRESSING, 6

mapping

32 or 48K, 12

memory

disabling blocks of, 12

#### Р

```

PAGE Ø, 7

PAGE Ø, 7

PHANTOM, 5, 12

board depopulation with, 12

POWER ON CLEAR, 4

PROMS

speed requirements of, 12

use of, 12

type necessary for substitution, 12

power requirements, 3

```

### <u>R</u>

RAM type of device, 3 RESET, 4

#### S

**SWO**, 14 special components, 3

# COMPONENT LAYOUT/SCHEMATIC

MM65K Memory Board Component Layout

@ 1981 G. MORROW

.